#### **SD9629 OVERVIEW**

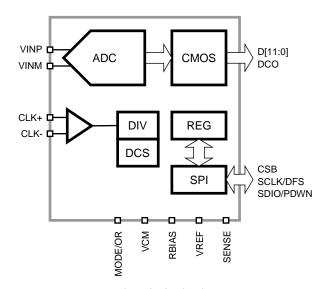

The SD9629 uses a multistage pipeline architecture to provide 12-bit accuracy at 20MSps data rates and to guarantee no missing codes over the full operating temperature range.

The SD9629 features internal references and can operate without an external reference or external common-mode bias.

Programming for configuration and control is accomplished using a 3-wire SPI-compatible interface. The digital output data can be programmed to be delivered in offset binary, gray code, or twos complement format. Further, to decrease EMI, the output data can be scrambled. A data output clock (DCO) is provided for each ADC channel to ensure proper timing at the receiver.

#### **FEATURES**

- SNR: 71.1dBFS at  $f_{IN}$  = 30.2MHz at  $f_{S}$  = 20MSps

- SFDR: 88.0dBc at  $f_{IN} = 30.2$ MHz at  $f_{S} = 20$ MSps

- -145.5dBFS/Hz input-noise at  $f_{\text{IN}}$  = 30.2MHz at  $f_{\text{S}}$  = 20MSps

- 2.0V<sub>p-p</sub> nominal input

- Integer 1-to-8 input clock divider (160MHz maximum input)

- · Sample rates of up to 20MSps

- 1.8V analog supply voltage

- Up to 3.3V digital I/O supply voltage

- · Internal ADC voltage reference

- · ADC clock duty cycle correction

- · Serial port control

- · Energy saving power-down modes

Figure 1: SD9629 Functional Block Diagram.

#### **APPLICATIONS**

- · Communications

- · General-purpose software radios

- Data acquisition systems (DAQ)

- · Process control Systems

- · Smart antenna systems

- · Multimode digital receivers

- · Ultrasound equipment

- Radar/LiDAR applications

# **Table of Contents**

| SPECIFICATIONS                      | 1  |

|-------------------------------------|----|

| DC Specifications                   | 1  |

| AC Specifications                   | 2  |

| Digital Specification               | 3  |

| Switching Specifications            | 5  |

| ABSOLUTE MAXIMUM RATINGS            | 6  |

| PACKAGE                             | 7  |

| TYPYCAL PERFORMANCE CHARACTERISTICS | 9  |

| EQUIVALENT CIRCUITS                 | 11 |

| THEORY OF OPERATION                 | 12 |

| ADC Architecture                    | 12 |

| Stand-by and Power-Down Modes       | 13 |

| Pin Functions                       | 13 |

| SERIAL PORT INTERFACE               | 15 |

| OUTPUT MODE                         | 17 |

| Data Scrambler                      | 17 |

| Alternate Bit Polarity              | 17 |

| Output Test Modes                   | 17 |

| CONTROL REGISTERS                   | 19 |

| ORDERING INFORMATION                | 25 |

| PACKAGE DRAWING                     | 26 |

| PEVISION HISTORY                    | 27 |

## **SPECIFICATIONS**

## **DC Specifications**

At  $T_A = 25$ °C,  $V_{AVDD} = 1.8V$ ,  $V_{DRVDD} = 1.8V$ ,  $F_{CLK} = 20$ MHz,  $A_{IN} = -1$ dBFS, differential AC-coupled sine wave external clock source, unless otherwise noted.

Table 1. DC Specifications.

| PARAMETER                  | TEMP | MIN     | TYP        | MAX  | UNIT     |

|----------------------------|------|---------|------------|------|----------|

| Resolution                 |      |         | 12         |      | bits     |

| Accuracy                   |      |         |            |      |          |

| No Missing Codes           | Full |         | Guaranteed |      |          |

| Offset Error               | Full | -0.50   |            | 0.50 | %FSR     |

| Gain Error                 | Full |         | 1.50       |      | %FSR     |

| DNL                        | Full |         |            | ±0.5 | LSB      |

| INL                        | Full |         |            | ±0.8 | LSB      |

| Matching                   |      |         |            |      |          |

| Offset Error               | 25°C | -0.70   |            | 0.70 | %FSR     |

| Gain Error                 | 25°C |         | 0.75       |      | %FSR     |

| Temperature Drift          |      |         |            |      |          |

| Offset Error               | Full |         | 0.05       |      | ppm/°C   |

| Gain Error                 | Full |         | 1.50       |      | ppm/°C   |

| Internal Voltage Reference |      |         |            |      |          |

| Output Voltage             | Full | 0.99    | 1.02       | 1.05 | V        |

| External Voltage Reference |      |         |            |      |          |

| Range                      | Full | 0.90    |            | 1.05 | V        |

| Input Referred Noise       |      |         |            |      |          |

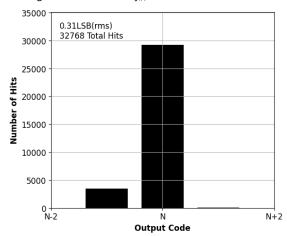

| $V_{REF} = 1.0V$           | 25°C |         | 0.34       |      | LSB(rms) |

| Analog Input               |      |         |            |      |          |

| Input Span, VREF = 1.0V    | Full |         | 2.0        |      | V        |

| Input Capacitance          | Full |         | 6.0        |      | pF       |

| Input Resistance           | Full |         | 2.0        |      | kΩ       |

| Input Common-Mode Voltage  | Full |         | 0.70       |      | V        |

| Input Common-Mode Range    | Full | 0.65    |            | 0.75 | V        |

| VCM Voltage                | Full |         | 0.70       |      | V        |

| VCM Current Capability     | Full |         | 100        |      | μΑ       |

| Reference Input Resistance | Full |         | 50         |      | kΩ       |

| Power Supply               |      |         |            |      |          |

| $V_{AVDD}$                 | Full | 1.7     | 1.8        | 1.9  | V        |

| $V_{DRVDD}$                | Full | 1.7     | 1.8        | 3.6  | V        |

| I <sub>AVDD</sub> @1.8V    | Full |         | 153.0      |      | mA       |

| I <sub>DRVDD</sub> @1.8V   | Full |         | 5.4        |      | mA       |

| Power Consumption          |      |         |            |      |          |

| Sine Wave Input            | Full |         | 286.1      |      | mW       |

| Standby <sup>1</sup>       | Full |         | 42.6       |      | mW       |

| Power Down                 | Full | <u></u> | 8.0        |      | mW       |

$<sup>^{\</sup>rm 1}\,{\rm Standby}$  power is measured with a sinewave input and active clock.

# **AC Specifications**

At  $T_A = 25$ °C,  $V_{AVDD} = 1.8V$ ,  $V_{DRVDD} = 1.8V$ ,  $F_{CLK} = 20$ MHz,  $A_{IN} = -1$ dBFS, differential AC-coupled sine wave external clock source, unless otherwise noted.

Table 2. AC Specifications.

| PARAMETER                                       | TEMP | MIN  | TYP   | MAX   | UNIT |

|-------------------------------------------------|------|------|-------|-------|------|

| Signal-to-Noise Ratio (SNR)                     |      |      |       |       |      |

| f <sub>IN</sub> = 6.55MHz                       | 25°C |      | 71.2  |       | dBFS |

| f <sub>IN</sub> = 30.2MHz                       | 25°C | 70.6 | 71.1  |       | dBFS |

|                                                 | Full | 70.4 |       |       | dBFS |

| f <sub>IN</sub> = 70.2MHz                       | 25°C |      | 70.7  |       | dBFS |

| f <sub>IN</sub> = 220MHz                        | 25°C |      | 68.3  |       | dBFS |

| Signal-to-Noise and Distortion Ratio (SNDR)     |      |      |       |       |      |

| f <sub>IN</sub> = 6.55MHz                       | 25°C |      | 70.7  |       | dBFS |

| f <sub>IN</sub> = 30.2MHz                       | 25°C | 70.1 | 70.6  |       | dBFS |

|                                                 | Full | 69.9 |       |       | dBFS |

| f <sub>IN</sub> = 70.2MHz                       | 25°C |      | 70.2  |       | dBFS |

| f <sub>IN</sub> = 220MHz                        | 25°C |      | 66.4  |       | dBFS |

| Effective Number of Bits (ENOB)                 |      |      |       |       |      |

| f <sub>IN</sub> = 6.55MHz                       | 25°C |      | 11.5  |       | bits |

| f <sub>IN</sub> = 30.2MHz                       | 25°C |      | 11.4  |       | bits |

| f <sub>IN</sub> = 70.2MHz                       | 25°C |      | 11.4  |       | bits |

| f <sub>IN</sub> = 220MHz                        | 25°C |      | 10.7  |       | bits |

| Worst Harmonic Power                            |      |      |       |       |      |

| f <sub>IN</sub> = 6.55MHz                       | 25°C |      | -89.0 |       | dBc  |

| f <sub>IN</sub> = 30.2MHz                       | 25°C |      | -88.0 | -82.0 | dBc  |

| f <sub>IN</sub> = 70.2MHz                       | 25°C |      | -86.0 |       | dBc  |

| f <sub>IN</sub> = 220MHz                        | 25°C |      | -71.0 |       | dBc  |

| Worst non-Harmonic Power                        |      |      |       |       |      |

| f <sub>IN</sub> = 6.55MHz                       | 25°C |      | -92.0 |       | dBc  |

| f <sub>IN</sub> = 30.2MHz                       | 25°C |      | -92.0 | -86.0 | dBc  |

| f <sub>IN</sub> = 70.2MHz                       | 25°C |      | -89.0 |       | dBc  |

| f <sub>IN</sub> = 220MHz                        | 25°C |      | -79.0 |       | dBc  |

| Spurious-Free Dynamic Range <sup>1</sup> (SFDR) |      |      |       |       |      |

| f <sub>IN</sub> = 6.55MHz                       | 25°C |      | 89.0  |       | dBc  |

| f <sub>IN</sub> = 30.2MHz                       | 25°C | 82.0 | 88.0  |       | dBc  |

|                                                 | Full | 81.0 |       |       | dBc  |

| f <sub>IN</sub> = 70.2MHz                       | 25°C |      | 86.0  |       | dBc  |

| f <sub>IN</sub> = 220MHz                        | 25°C |      | 71.0  |       | dBc  |

| Two-Tone SFDR                                   |      |      |       |       |      |

| $f_{IN1} = 29.1MHz, f_{IN2} = 30.6MHz$          | 25°C |      | 88.0  |       | MHz  |

| Analog Input Bandwidth                          | Full |      | 650.0 |       | MHz  |

$<sup>^{\</sup>rm 1}\,\text{SFDR}$  excludes the DC and  $f_{\rm s}/2$  bins.

# **Digital Specification**

$V_{AVDD}$  = 1.8V,  $V_{DRVDD}$  = 1.8V,  $F_{CLK}$  = 20MHz,  $A_{IN}$  = -1dBFS, differential AC-coupled sine wave external clock source, DCS enabled, unless otherwise noted.

Table 3. Differential Clock Input.

| PARAMETER                  | TEMP | MIN                    | TYP        | MAX                    | UNIT      |

|----------------------------|------|------------------------|------------|------------------------|-----------|

| Logic Compliance           | Full | СМО                    | S/LVDS/LVF | PECL                   |           |

| Internal Common-Mode Bias  | Full |                        | 0.9        |                        | V         |

| Differential Input Voltage | Full | 0.3                    |            | 3.6                    | $V_{p-p}$ |

| Input Voltage Range        | Full | V <sub>AGND</sub> -0.3 |            | V <sub>AVDD</sub> +0.2 | V         |

| Input Common-Mode Range    | Full | 0.75                   |            | 1.05                   | V         |

| High Level Input Current   | Full | -10                    |            | 10                     | μΑ        |

| Low Level Input Current    | Full | -10                    |            | 10                     | μΑ        |

| Input Capacitance          | Full |                        | 1.7        |                        | pF        |

| Input Resistance           | Full |                        | 6          |                        | kΩ        |

#### Table 4. CSB Input.

| PARAMETER                | TEMP | MIN  | TYP | MAX | UNIT |

|--------------------------|------|------|-----|-----|------|

| High Level Input Voltage | Full | 1.22 |     |     | V    |

| Low Level Input Voltage  | Full |      |     | 0.6 | V    |

| High Level Input Current | Full | -1   |     | 1   | μΑ   |

| Low Level Input Current  | Full | -1   |     | 1   | μΑ   |

| Input Capacitance        | Full |      | 1.5 |     | pF   |

| Input Resistance         | Full |      | 15  |     | kΩ   |

## Table 5. SCLK/DFS Input.

| PARAMETER                | TEMP | MIN  | TYP | MAX | UNIT |

|--------------------------|------|------|-----|-----|------|

| High Level Input Voltage | Full | 1.22 |     |     | V    |

| Low Level Input Voltage  | Full |      |     | 0.6 | V    |

| High Level Input Current | Full | -1   |     | 1   | μΑ   |

| Low Level Input Current  | Full | -1   |     | 1   | μΑ   |

| Input Capacitance        | Full |      | 1.5 |     | pF   |

| Input Resistance         | Full |      | 15  |     | kΩ   |

## Table 6. SDIO/PDWN Input.

| PARAMETER                | TEMP | MIN  | TYP | MAX | UNIT |

|--------------------------|------|------|-----|-----|------|

| High Level Input Voltage | Full | 1.22 |     |     | V    |

| Low Level Input Voltage  | Full |      |     | 0.6 | V    |

| High Level Input Current | Full | -1   |     | 1   | μΑ   |

| Low Level Input Current  | Full | -1   |     | 1   | μΑ   |

| Input Capacitance        | Full |      | 1.5 |     | pF   |

| Input Resistance         | Full |      | 15  |     | kΩ   |

# Table 7. CMOS Outputs (DATA and OR).

| PARAMETER                        | TEMP | MIN  | TYP | MAX  | UNIT |

|----------------------------------|------|------|-----|------|------|

| DRVDD = 3.3V                     |      |      |     |      |      |

| High Level Output Voltage @50µA  | Full | 3.2  |     |      | V    |

| High Level Output Voltage @0.5mA | Full | 3.1  |     |      | V    |

| Low Level Output Voltage @50µA   | Full |      |     | 0.05 | V    |

| Low Level Output Voltage @1.6mA  | Full |      |     | 0.1  | V    |

| DRVDD = 1.8V                     |      |      |     |      |      |

| High Level Output Voltage @50µA  | Full | 1.75 |     |      | V    |

| High Level Output Voltage @0.5mA | Full | 1.7  |     |      | V    |

| Low Level Output Voltage @50µA   | Full |      |     | 0.05 | V    |

| Low Level Output Voltage @1.6mA  | Full |      |     | 0.2  | V    |

# **Switching Specifications**

$V_{AVDD}$  = 1.8V,  $V_{DRVDD}$  = 1.8V,  $F_{CLK}$  = 20MHz,  $A_{IN}$  = -1dBFS, differential AC-coupled sine wave external clock source, DCS enabled, unless otherwise noted.

Table 8. Clock Input Timing.

| PARAMETER                                      | TEMP                              | MIN   | TYP  | MAX   | UNIT |

|------------------------------------------------|-----------------------------------|-------|------|-------|------|

| Input Clock Rate                               | Full                              |       |      | 160.0 | MHz  |

| Conversion Rate (after clock divider)          | te (after clock divider) Full 3.0 |       |      |       | MHz  |

| CLK Pulse Width High (t <sub>CH</sub> )        |                                   |       |      |       |      |

| Divide-by-1 Mode, DCS Enabled                  | Full                              | 1.5   |      |       | ns   |

| Divide-by-1 Mode, DCS Disabled                 | Full                              | 22.0  | 25.0 | 28.0  | ns   |

| Divide-by-2 Mode Through Divide-by-8 Mode      | Full                              | 1.5   |      |       | ns   |

| Aperture Delay (t <sub>A</sub> )               | Full                              |       | 0.5  |       | ns   |

| Aperture Uncertainty (Jitter, t <sub>J</sub> ) | Full                              | 140.0 |      |       | fs   |

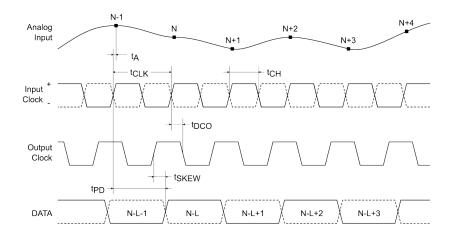

Table 9. Data Output.

| PARAMETER                                 | TEMP | MIN | TYP   | MAX | UNIT   |

|-------------------------------------------|------|-----|-------|-----|--------|

| CMOS Mode                                 |      |     |       |     |        |

| Data Propagation Delay (t <sub>PD</sub> ) | Full |     | 5.5   |     | ns     |

| DCO Propagation Delay (t <sub>DCO</sub> ) | Full |     | 6.5   |     | ns     |

| DCO to Data Skew (t <sub>SKEW</sub> )     | Full |     | -1.0  |     | ns     |

| Pipeline Delay (Latency, L)               | Full |     | 35    |     | Cycles |

| Wake-Up Time (from sleep)                 | Full |     | 5     |     | μs     |

| Wake-Up Time (from power down)            | Full |     | 600.0 |     | μs     |

| Out-of-Range Recovery Time                | Full |     | 3     |     | Cycles |

Figure 2: Parallel CMOS Output Mode Timing.

#### **ABSOLUTE MAXIMUM RATINGS**

Table 10. Absolute Maximum Ratings ( $T_A = 25$ °C, unless otherwise specified).

| Parameter                               | Symbol      | Conditions       | Min  | Max | Units |

|-----------------------------------------|-------------|------------------|------|-----|-------|

| AVDD                                    | $V_{AVDD}$  | Relative to AGND | -0.3 | 2.0 | V     |

| DRVDD                                   | $V_{DRVDD}$ | Relative to AGND | -0.3 | 3.8 | V     |

| VINP, VINM                              |             | Relative to AGND | -0.3 | 2.0 | V     |

| CLK+, CLK-                              |             | Relative to AGND | -0.3 | 2.0 | V     |

| RBIAS                                   |             | Relative to AGND | -0.3 | 2.0 | V     |

| SENSE                                   |             | Relative to AGND | -0.3 | 2.0 | V     |

| VCM                                     |             | Relative to AGND | -0.3 | 2.0 | V     |

| VREF                                    |             | Relative to AGND | -0.3 | 2.0 | V     |

| CSB                                     |             | Relative to AGND | -0.3 | 3.8 | V     |

| SCLK/DFS                                |             | Relative to AGND | -0.3 | 3.8 | V     |

| SDIO/PDWN                               |             | Relative to AGND | -0.3 | 3.8 | V     |

| MODE/OR                                 |             | Relative to AGND | -0.3 | 3.8 | V     |

| D0,, D11                                |             | Relative to AGND | -0.3 | 3.8 | V     |

| DCO                                     |             | Relative to AGND | -0.3 | 3.8 | V     |

| Operating Temperature Range (Ambient)   |             |                  | -40  | 85  |       |

| Maximum Junction Temperature Under Bias |             |                  |      | 125 | °C    |

| Storage Temperature Range (Ambient)     |             |                  | -65  | 150 |       |

#### Notes:

Stresses beyond those listed under Table 10 may cause permanent damage to the device. These are stress ratings only

and functional operation of the device at these or any other conditions beyond those indicated under recommended

operating conditions is not implied. Exposure to absolute–maximum–rated conditions for extended periods may affect

device reliability.

#### **ESD CAUTION.**

**Electrostatic Discharge Sensitive Device.**

Proper ESD precautions should be observed to prevent performance degradation or loss of functionality.

#### **PACKAGE**

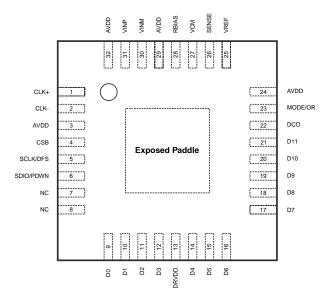

Figure 3: SD9629 Package Top View.

- 1. NC = No Connect.

- 2. The exposed thermal pad on the bottom of the package provides the analog ground for the part and must be connected for proper operation.

Table 11. Pin Descriptions.

| Number | Name      | Туре   | Comment                                                       |

|--------|-----------|--------|---------------------------------------------------------------|

| 0      | AGND      | Ground | Exposed Paddle, Analog Ground.                                |

| 1      | CLK+      | Input  | ADC Clock Input (Plus).                                       |

| 2      | CLK-      | Input  | ADC Clock Input (Minus).                                      |

| 3      | AVDD      | Power  | Analog Power Supply (1.8 V Nominal).                          |

| 4      | CSB       | Input  | SPI Chip Select (Active Low).                                 |

| 5      | SCLK/DFS  | Input  | SPI Serial Clock/Data Format Select Pin in External Pin Mode. |

| 6      | SDIO/PDWN | InOut  | SPI Serial Data I/O. Power Down Pin in External Pin Mode.     |

| 7      | NC        |        | Do Not Connect.                                               |

| 8      | NC        |        | Do Not Connect.                                               |

| 9      | D0        | Output | Output Data 0.                                                |

| 10     | D1        | Output | Output Data 1.                                                |

| 11     | D2        | Output | Output Data 2.                                                |

| 12     | D3        | Output | Output Data 3.                                                |

| 13     | DRVDD     | Power  | Digital I/O Supply.                                           |

| 14     | D4        | Output | Output Data 4.                                                |

| 15     | D5        | Output | Output Data 5.                                                |

| 16     | D6        | Output | Output Data 6.                                                |

| 17     | D7        | Output | Output Data 7.                                                |

| 18     | D8        | Output | Output Data 8.                                                |

| 19     | D9        | Output | Output Data 9.                                                |

| 20     | D10       | Output | Output Data 10.                                               |

| Number | Name    | Туре   | Comment                                                                                             |

|--------|---------|--------|-----------------------------------------------------------------------------------------------------|

| 21     | D11     | Output | Output Data 11.                                                                                     |

| 22     | DCO     | Output | Clock Output.                                                                                       |

| 23     | MODE/OR | InOut  | Chip Mode Select Input (MODE)/Out-of-Range Digital Output in SPI Mode (OR).                         |

| 24     | AVDD    | Power  | Analog Power Supply (1.8 V Nominal).                                                                |

| 25     | VREF    | InOut  | Voltage Reference Input/Output.                                                                     |

| 26     | SENSE   | Input  | Reference Programming Pin.                                                                          |

| 27     | VCM     | Output | This pin outputs the common-mode voltage that can be used externally to bias the analog input pins. |

| 28     | RBIAS   | InOut  | External Reference Bias Resistor. Connect to $30k\Omega$ (1% tolerance) resistor to ground.         |

| 29     | AVDD    | Power  | Analog Power Supply (1.8 V Nominal).                                                                |

| 30     | VINM    | Input  | Differential Analog Input Pin (Minus).                                                              |

| 31     | VINP    | Input  | Differential Analog Input Pin (Plus).                                                               |

| 32     | AVDD    | Power  | Analog Power Supply (1.8 V Nominal).                                                                |

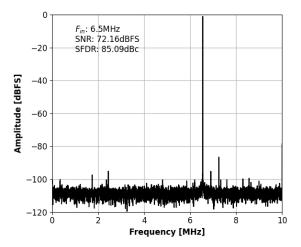

#### TYPYCAL PERFORMANCE CHARACTERISTICS

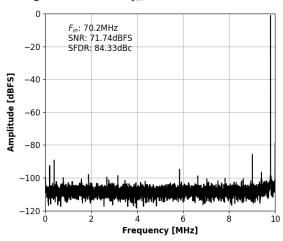

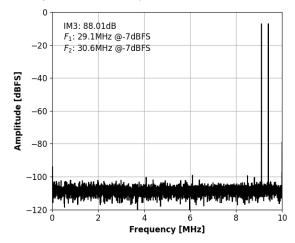

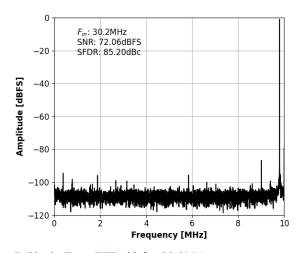

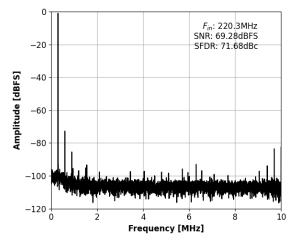

At  $T_A = 25$ °C,  $V_{AVDD} = 1.8V$ ,  $V_{DRVDD} = 1.8V$ ,  $F_{CLK} = 20$ MHz,  $A_{IN} = -1$ dBFS, differential AC-coupled clock source, unless otherwise noted.

Figure 4: Single-Tone FFT with  $f_{IN}$ =6.55MHz.

Figure 6: Single-Tone FFT with  $f_{IN}$ =70.2MHz.

Figure 8: Two-Tone FFT with  $f_{\text{IN1}}$ =29.1MHz,  $f_{\text{IN2}}$ =30.6MHz.

Figure 5: Single-Tone FFT with  $f_{IN}$ =30.2MHz.

Figure 7: Single-Tone FFT with  $f_{IN}$ =220MHz.

Figure 9: Grounded Input Histogram.

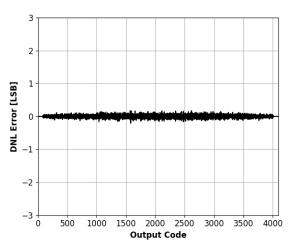

Figure 10: DNL Error with  $f_{\text{IN}}$ =6.55MHz.

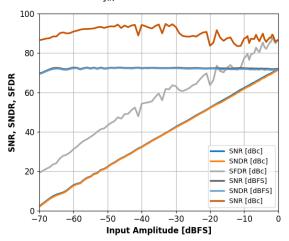

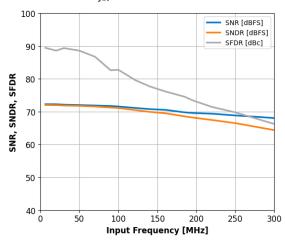

Figure 12: Single-Tone SNR, SNDR and SFDR vs. Input Amplitude Figure 13: Single-Tone SNR, SNDR and SFDR vs. Input with  $f_{IN}$ =30.2MHz.

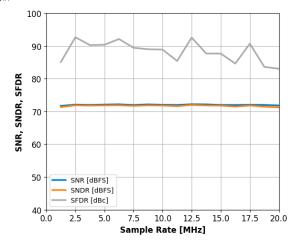

Figure 14: Single-Tone SNR, SNDR and SFDR vs. Sample Rate with  $f_{IN}$ =30.2MHz.

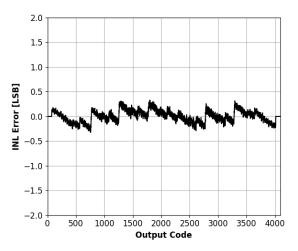

Figure 11: INL Error with  $f_{IN}$ =6.55MHz.

Frequency with  $f_s$ =20MHz.

# **EQUIVALENT CIRCUITS**

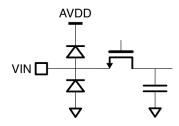

Figure 16: Equivalent Analog Input Circuit.

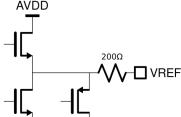

AVDD

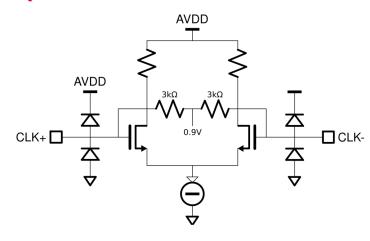

Figure 15: Equivalent Clock Input Circuit.

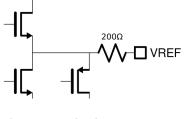

Figure 17: Equivalent VREF Circuit.

**√**/-□ ∨CM

Figure 18: Equivalent VCM Circuit.

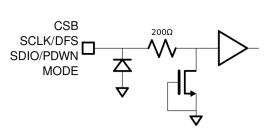

Figure 19: Equivalent CSB, SCLK/DFS, SDIO/PDWN or MODE Input Circuit.

Figure 20: Equivalent Digital Output Circuit.

#### THEORY OF OPERATION

#### **ADC Architecture**

The ADC uses a pipelined architecture and innovative patented switched-capacitor circuits. The differential implementation makes it highly immune to power supply noise and reference voltage self-modulation.

## **Analog Input**

The input stage behaves as a switched-capacitor network, presenting itself to the driving circuit as a combination of a switch and a sampling capacitor. The capacitor is reset prior to each conversion cycle, effectively eliminating non-linear memory effects commonly observed in some pipelined ADC architectures. The ADC does not include an internal commonmode bias therefore, the driving source must provide an appropriate common-mode voltage.

## **Differential Clock Input**

The SD9629 features a differential clock receiver with an integrated common-mode bias. For proper operation, the clock inputs should be AC-coupled using 10nF capacitors.

**Differential Clock Configuration.** For optimal jitter performance, a differential clock source is recommended. Connect the differential clock signals to CLK+ and CLK- through 10nF AC-coupling capacitors.

**Single-Ended Clock Configuration.** If a single-ended clock source is used, AC-couple the signal to the CLK+ pin. In this configuration, connect a 10nF capacitor between the CLK- pin and analog ground to maintain proper biasing.

**Clock Jitter Considerations.** Clock jitter has a significant impact on the ADC's signal-to-noise ratio (SNR). The sensitivity to jitter increases with input signal frequency. For best performance, use a low-noise differential clock with fast edge transitions.

**Note**: In some conditions the part can enter in manufacturing test mode if both differential clock inputs are held low for more than 1ms. This behavior can be blocked by writing 1 to register *0x4cf*, bit[15].

#### **Clock Divider**

The ADC includes a programmable clock divider that allows the input clock to be divided by integer values from 2 to 8. The divider is configured by setting register 0x463, bits [7:5], to the desired division value. A value of 0 (default) bypasses the divider entirely.

By default, the divider starts asynchronously.

**Clock Duty-Cycle Requirements.** The ADC utilizes both the rising and falling edges of the input clock (or the divided clock, if the divider is enabled) for internal sampling operations. To achieve optimal performance — especially at the maximum sampling rate — the clock duty cycle should be as close to 50% as possible.

When the divider is enabled with an even divisor, a 50% duty cycle is guaranteed by design. If the application uses a clock with a non-ideal duty cycle, a Duty Cycle Stabilizer (DCS) can be enabled to improve performance.

#### **ADC Self-Calibration**

The ADC includes an automatic calibration mechanism that is executed at power-up to ensure optimal performance. For best results, calibration should be performed at the actual sampling rate used during operation. To support this, the device continuously monitors the sampling clock frequency and automatically re-triggers calibration if a significant change is detected. This feature can be disabled by setting bit[0] of the *0x4c9* register to 1.

Manual calibration can also be initiated by toggling *0xcc1*, bit[4] from 0 to 1. The calibration process is implemented using a state-machine architecture, ensuring a deterministic and predictable calibration time.

In addition, the ADC supports a Background Calibration (BGC) mode, which is disabled by default. BGC is beneficial in environments with large temperature variations near the extremes of the specified operating temperature range. When enabled, BGC injects a dither signal into the ADC input path, improving performance under thermal stress. However, this

dither consumes approximately 0.8dB of the ADC's input range, resulting in earlier clipping compared to when BGC is disabled.

To enable BGC, set the following bits to 1:

- 0xce1, bit[15]

- 0xce3, bit[3]

After enabling these bits, manually trigger calibration as described above.

## **Stand-by and Power-Down Modes**

The SD9629 supports two power-saving modes that can be used when the ADC is not actively sampling. In both modes, the SPI interface (if enabled) remains operational.

**Power-Down Mode.** This mode disables most of the internal circuitry, resulting in the lowest residual supply current. It is ideal for applications requiring minimal power consumption during idle periods. Power-down mode can be enabled via:

- · The PDWN pin (when available), or

- Setting register 0x457, bit[7], to 1.

**Standby Mode.** Standby mode offers a faster wake-up time compared to power-down mode, at the cost of slightly higher residual current. It is suitable for applications that require rapid recovery from idle states. To enable standby mode, set register *0x457*, bits [3] and [8], to 1.

**Note**: It is recommended to disable the ADC auto-calibration when using standby mode to avoid unintended calibration cycles during transitions.

#### **Pin Functions**

The SD9629 offers several functions available via dual function pin controls (external pin mode vs. SPI mode). The SD9629 detects the SPI mode during the first SPI transaction after power-up. If the user does not want to program the device via the SPI interface, the dual function is available.

#### **DFS**

Data Format Select can be used to select between offset binary or two's complement when operating in the external pin mode.

#### **RBIAS**

External Reference Bias Resistor. The SD9629 requires a  $30k\Omega$ , 1% resistor, between pin RBIAS and AGND to set the default bias current for the ADC.

#### **VCM**

Common-Mode Level Bias Output for Analog Input. The VCM pin provides a DC voltage that can be used to bias the ADC input common-mode level, either directly using a passive circuit or indirectly as a common-mode reference voltage for the driving active device. In most use cases, the default common-mode voltage level is optimal.

### **VREF**

The ADC supports both internal (default) and external voltage reference sources, selectable via the VREF pin. The selection between internal and external reference voltage can be made in one of two ways:

- Using the SENSE pin: a logic high level selects the external reference.

- Via register control: setting register 0x45d, bit[5] to 1 selects the external reference.

Internal Reference Output. When the internal voltage reference is used, the VREF pin can function as a reference output.

This output can be enabled by setting register 0x45d, bits [11:10], to 0x3.

If the SENSE pin is held low, the reference output is enabled by default. To disable the reference output in this configuration, set register 0x45d, bits [11:10], to 0x2.

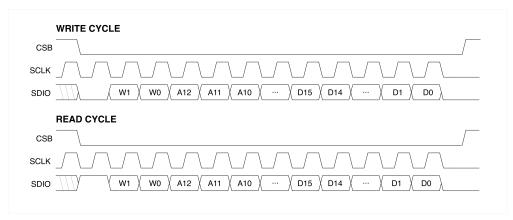

#### SERIAL PORT INTERFACE

The SD9629 uses a 3-wire Serial Port Interface (SPI) that gives the user flexibility to configure the converter for specific functions, depending on the application, through a register space provided inside the ADC.

The interface signals are:

- SCLK defines the bit rate at which serial data is driven onto, and sampled from, the bus;

- CSB defines the boundaries of a basic data 'unit', comprised of multiple serial bits;

- · SDIO is the serial data IO wire;

The read and write cycles are described in the figure below. The complete instruction cycle is 32-bits long. The falling edge of CSB combines with the rising edge of SCLK marks the start of the instruction cycle. The address space is 13 bits long (A<12:0>) and the data is 16 bits wide (D<15:0>).

Figure 21: 3-wire SPI timing.

Table 12. SPI Timing.

| PARAMETER                                                                                             | SYMBOL                      | MIN | TYP | MAX | UNIT |

|-------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----|-----|------|

| Setup time between the data and the rising edge of SCLK                                               | t <sub>DS</sub>             | 2   |     |     | ns   |

| Hold time between the data and the rising edge of SCLK                                                | t <sub>HD</sub>             | 2   |     |     | ns   |

| Period of the SCLK                                                                                    | t <sub>sclk</sub>           | 40  |     |     | ns   |

| Setup time between CSB and SCLK                                                                       | t <sub>s,csb-sclk</sub>     | 2   |     |     | ns   |

| Hold time between CSB and SCLK                                                                        | t <sub>H,CSB-SCLK</sub>     | 2   |     |     | ns   |

| Minimum period that SCLK should be in a logic high state                                              | t <sub>SCLK,high</sub>      | 10  |     |     | ns   |

| Minimum period that SCLK should be in a logic low state                                               | t <sub>SCLK,low</sub>       | 10  |     |     | ns   |

| Time required for the SDIO pin to switch from an input to an output relative to the SCLK falling edge | $t_{\text{SDIO},\text{EN}}$ | 10  |     |     | ns   |

| Time required for the SDIO pin to switch from an output to an input relative to the SCLK rising edge  | t <sub>sDIO,DIS</sub>       | 10  |     |     | ns   |

The falling edge of CSB, in conjunction with the rising edge of SCLK, determines the start of the framing.

Two bits, W1 and W0, determine how many bytes of data that can be transferred in the same write cycle (see Table 13). If more than 16 bits (2 Bytes) of data are being transferred the address is increased sequentially.

## Table 13. SPI Word Length.

| [W1,W0] | Data length                           |

|---------|---------------------------------------|

| 00      | Not supported                         |

| 01      | Two bytes of data can be transferred  |

| 10      | Not supported                         |

| 11      | Four bytes of data can be transferred |

The SPI pins should not be active when the full dynamic performance of the ADC is required. Noise from SCLK, CSB and the data transactions can degrade ADC performance.

#### **OUTPUT MODE**

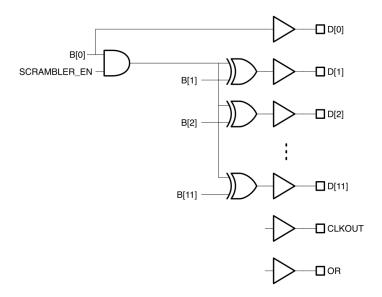

#### **Data Scrambler**

Interference originating from the digital outputs of the ADC can be difficult to eliminate entirely. Such interference may result from capacitive or inductive coupling mechanisms, or from shared impedance paths in the ground plane. Even minimal coupling coefficients can introduce deterministic spurious tones into the ADC's output frequency spectrum. To mitigate this, digital output scrambling techniques can be employed prior to off-chip transmission. By randomizing the bit patterns, the spectral energy of these spurs is dispersed, effectively reducing their peak amplitudes and minimizing their impact on signal integrity.

The SD9629 can apply an exclusive-OR logic operation between the LSB and all other data output bits, while the LSB, overflow and clock outputs are not affected.

When this function is used, the receiver must apply the same function to unscramble the received data.

The data scrambler is enabled by programming control register 0x4b5, bit[13].

Figure 22: SD9629 Data Scrambler.

#### **Alternate Bit Polarity**

The alternate bit polarity is particularly effective to suppress digital feedback and minimize noise coupling on the PCB when the ADC input signal is near mid-scale and of very small amplitude. In this case, the digital output tends to toggle between patterns dominated by either logic high or logic low states. This synchronized switching of multiple bits can induce significant transient currents in the ground plane, leading to increased digital noise. This mode, when activated, inverts all odd-numbered data output bits prior to the output buffer stage while even-numbered bits, along with the overflow and clock output, remain unaffected thus ensuring that approximately half of the output bits transition are high while the other half transition are low. This balanced switching behavior helps cancel out opposing current flows in the ground return path, thereby reducing overall ground noise. At the receiving end, the original data can be reconstructed by inverting the same odd-numbered bits. This mode operates independently of the digital output randomization feature—both functions can be enabled or disabled separately. The Alternate Bit Polarity mode is configured via serial programming of control register *0x4b5*, bit[14].

#### **Output Test Modes**

The output test options are described in Table 14 and are selected via SPI programming at register 0x4b5, bits [5:2].

When an output test mode is enabled, the analog section of the ADC is disconnected from the digital back-end blocks and the test pattern is run through the output formatting block. These tests require an active input clock.

There are two pseudo-random number generators available, PN23 and PN9. The PN23 generator ( $X^{23}+X^{18}+1$ ), selected by register 0x4b5, bits [5:2], set to 0x5, can be reset by setting register 0x4b5, bit [12], low; while the PN9 generator ( $X^9+X^5+1$ ), selected by register 0x4b5 set to 0x6, can be reset by setting register 0x4b5, bit [11], low.

Table 14. Output Test Modes.

| Mode | Function        |

|------|-----------------|

| 0    | Pass-Through    |

| 1    | Midscale        |

| 2    | +FS             |

| 3    | -FS             |

| 4    | Checkerboard    |

| 5    | PN23            |

| 6    | PN9             |

| 7    | 1/0 word toggle |

| 8    | User input      |

| 9    | 1/0 bit toggle  |

| 10   | 1x sync         |

| 11   | 1-bit high      |

| 12   | Mixed frequency |

| 13   | Unused          |

| 14   | Unused          |

| 15   | Ramp            |

Pass-through and test patterns 1, 2, 3, 5 and 6 are subject to output formatting, while the other test modes are not. Test patterns 1, 8 and 15 can be applied to either one channel or both channels using 0x4b5, bit[7:6]. Patterns 4 and 7 can be toggled between the pattern and its inverse while test pattern 8 can be selected using registers 0x4bb, 0x4bd, [DB\_TEST0\_register] and [DB\_TEST1\_register].

#### **CONTROL REGISTERS**

The following tables describe the control registers. The tables describe the registers as follows:

| Address: <hex value=""></hex> |         | RW or RO       | Default: <hex value=""></hex> |

|-------------------------------|---------|----------------|-------------------------------|

| bit field                     | default | field descript | ion.                          |

|                               | value   |                |                               |

where: **RW** indicates a Read/Write register and **RO** indicates a Read-Only register. If the register is read-only, the default value is omitted.

Registers not explicitly described in the following tables should not be written.

When changing control register values, read-modify-write procedure should be used. Some registers contain reserved bit fields for engineering purposes. This avoids inadvertently changing the values of those bits.

| Address: | 0x455 | RW                       | Default: 0x1                                                                                                   |

|----------|-------|--------------------------|----------------------------------------------------------------------------------------------------------------|

| [0]      | 0x1   | Soft reset (active low). |                                                                                                                |

|          |       | l =                      |                                                                                                                |

| Address: | 0x457 | RW                       | Default: 0x015                                                                                                 |

| [0]      | 0x1   | Duty Cycle               | e Stabilizer enable.                                                                                           |

| [1]      | 0x0   | Duty Cycle               | e Stabilizer.                                                                                                  |

| [2]      | 0x1   | External o               | utput enable (OE/OEB) control                                                                                  |

|          |       |                          | t Enabled                                                                                                      |

| -        |       | 1: Output                | t depends on pin OE/OEB                                                                                        |

| [3]      | 0x0   | Output dis               |                                                                                                                |

|          |       |                          | t depends on oeb_en_reg (default)                                                                              |

|          |       | 1: Disabl                | ed                                                                                                             |

| [4]      | 0x1   | Reserved.                |                                                                                                                |

| [6:5]    | 0x0   | Reserved.                |                                                                                                                |

| [7]      | 0x0   | Software p               | oower down.                                                                                                    |

| [8]      | 0x0   | Software s               | leep mode.                                                                                                     |

| Address: | 0x45d | RW                       | Default: 0x0095                                                                                                |

| [0]      | 0x1   | Reference                | enable.                                                                                                        |

| [4:1]    | 0xa   | Reference                | value.                                                                                                         |

| [5]      | 0x0   | Set reference.           |                                                                                                                |

|          |       | 0: Interna               | al entre de la companya de la compa |

|          |       | 1: Extern                | al                                                                                                             |

| [9:6]    | 0x2   | Reserved.                |                                                                                                                |

| [11:10]  | 0x0   | Reserved.                |                                                                                                                |

| [14:12]  | 0x0   | Reserved.                |                                                                                                                |

| Address: 0 | x463                             | RW                                                         | Default: 0x019   |  |

|------------|----------------------------------|------------------------------------------------------------|------------------|--|

| [0]        | 0x1                              | Enable clock receiver.                                     |                  |  |

| [2:1]      | 0x0                              | Clock RX cc                                                | ommon-mode bias. |  |

| [4:3]      | 0x3                              | Clock RX bia                                               | as.              |  |

| [7:5]      | 5] 0x0 Clock RX divider control. |                                                            | vider control.   |  |

|            |                                  | 0: Bypass                                                  |                  |  |

|            |                                  | 1: Divide by 2                                             |                  |  |

|            |                                  | 2: Divide b                                                | y 3              |  |

|            |                                  | 3:<br>7: Divide by 8                                       |                  |  |

| [0]        | 0.40                             |                                                            |                  |  |

| [8]        | 0x0                              |                                                            | hip termination. |  |

| [9]        | 0x0                              | Clock RX po                                                | рапту.           |  |

| [10]       | 0x0                              | Reserved.                                                  |                  |  |

| Address: 0 | v/65                             | RW                                                         | Default: 0x0     |  |

| [2:0]      | 0x0                              |                                                            |                  |  |

| [2.0]      | OXO                              | Output data interleaver.  0: pass through, no interleaving |                  |  |

|            |                                  | 1: pass through, channels swapped, no interleaving         |                  |  |

|            |                                  | 2: N/A                                                     |                  |  |

|            |                                  | 3: N/A                                                     |                  |  |

|            |                                  | 4: Reserved                                                |                  |  |

|            |                                  | 5: Reserved                                                |                  |  |

|            |                                  | 6: even-odd interleaving                                   |                  |  |

|            |                                  | 7: odd-even interleaving                                   |                  |  |

| Address: 0 | x473                             | RW                                                         | Default: 0x0000  |  |

| [4:0]      | 0x00                             | Reserved.                                                  |                  |  |

| [9:5]      | 0x00                             | Output data delay.                                         |                  |  |

| [14:10]    | 0x00                             | Output clock delay.                                        |                  |  |

| [==0]      | 1 3,000                          | T Satpat Slooi                                             | . a.s.a., .      |  |

| Address: 0 | x475                             | RW                                                         | Default: 0x1     |  |

| [0]        | 0x1                              | Enable VCM                                                 | 1.               |  |

| Address: 0     | x4b5           | RW                                                                  | Default: 0x18c0                                       |  |  |

|----------------|----------------|---------------------------------------------------------------------|-------------------------------------------------------|--|--|

| [1:0]          | 0x0            | Output form<br>0: Signed b<br>1: Offset bi<br>2: Gray coo<br>3: N/A | nary                                                  |  |  |

| [5:2]          | 0x0            | Output test r                                                       | mode select (see Table 14).                           |  |  |

| [6]            | 0x1            | Output test of 0: Disable 1: Enable                                 | channel.                                              |  |  |

| [7]            | 0x1            | Reserved.                                                           |                                                       |  |  |

| [8]            | 0x0            | Output test t                                                       | oggle mode. Toggle between user test pattern 0 and 1. |  |  |

| [10:9]         | 0x0            | ·                                                                   | 2'h2:                                                 |  |  |

| [11]           | 0x1            | PN9 genera                                                          | tor reset (active low)                                |  |  |

| [12]           | 0x1            | PN23 gener                                                          | ator reset (active low)                               |  |  |

| [13]           | 0x0            | Enable the c                                                        | Enable the output data scrambler.                     |  |  |

| [14]           | 0x0            | Enable alter                                                        | nate bit polarity switch.                             |  |  |

| Address: 0     | Address: 0x4b7 |                                                                     | Default: 0x0092                                       |  |  |

| [15:0]         | 0x0092         | PN9 initial se                                                      | eed.                                                  |  |  |

| Address: 0     | x4b9           | RW                                                                  | Default: 0x3aff                                       |  |  |

| [15:0]         | 0x3aff         | PN9 initial se                                                      | eed.                                                  |  |  |

| Address: 0     | x4bb           | RW                                                                  | Default: 0x0000                                       |  |  |

| [15:0]         | 0x0000         | User test par                                                       | ttern 0.                                              |  |  |

| Address: 0     | x4bd           | RW                                                                  | Default: 0x0000                                       |  |  |

| [15:0]         | 0x0000         | User test pattern 1.                                                |                                                       |  |  |

| Address: 0x4c9 |                | RW                                                                  | Default: 0x0000                                       |  |  |

| [0]            | 0x0            | Disable auto-recalibration.                                         |                                                       |  |  |

| [15:1]         | 0x0000         | Reserved.                                                           |                                                       |  |  |

| Address: 0     |                | RW                                                                  | Default: 0x0035                                       |  |  |

| [14:0]         | 0x0035         | Reserved.                                                           |                                                       |  |  |

| [15]           | 0x0035         | Disable test                                                        | mode.                                                 |  |  |

21 | Datasheet www.silannasemi.com Doc. No. 11724, Rev. 2.0

| Address:   | 0x4fd         | RO                                                    | Default: N/A         |  |  |

|------------|---------------|-------------------------------------------------------|----------------------|--|--|

| [2:0]      |               | Chip revision.                                        |                      |  |  |

| [6:3]      |               | Label ID.                                             |                      |  |  |

| [7]        |               | Reserved.                                             |                      |  |  |

| [8]        |               | Reserved.                                             |                      |  |  |

| [10:9]     |               | Resolution ID 0: 10-bit 1: 12-bit 2: 14-bit 3: 16-bit | O for device         |  |  |

| [13:11]    |               | Speed ID for                                          | device.              |  |  |

| Address:   | 0x4ff         | RO                                                    | Default: N/A         |  |  |

| [0]        |               | Reserved.                                             |                      |  |  |

| [1]        |               | Analog Supp                                           | ly Ready.            |  |  |

| [2]        |               | Digital Supply                                        | y Ready.             |  |  |

| [3]        |               | I/O Supply Re                                         | eady.                |  |  |

| [4]        |               | Sense pin sta                                         | atus.                |  |  |

| [5]        |               | SPI enabled.                                          |                      |  |  |

| [6]        |               | Reserved.                                             |                      |  |  |

| [7]        |               | Reserved.                                             |                      |  |  |

| [8]        |               | Reserved.                                             |                      |  |  |

| [9]        |               | Reserved.                                             |                      |  |  |

| [10]       |               | Reserved.                                             |                      |  |  |

| Address: ( | nvf02         | RW                                                    | Default: 0x7f8       |  |  |

| [0]        | 0x0           | Enable top le                                         |                      |  |  |

| [1]        | 0x0           |                                                       | skew control DAC.    |  |  |

| [2]        | 0x0           | Reserved.                                             | Show solition by to. |  |  |

| [3]        | 0x1           | Reserved.                                             |                      |  |  |

| [4]        | 0x1           | Reserved.                                             |                      |  |  |

| [10:5]     | 0x3f          | Mask for ena                                          | ble pin.             |  |  |

|            | 1             | 1                                                     | •                    |  |  |

| Address:   | 0xf05         | RW                                                    | Default: 0x30        |  |  |

| [5:0]      | 0x30          | Mask for slee                                         | ep pin.              |  |  |

| [6]        | [6] 0x0 Sleep |                                                       | Sleep ADC.           |  |  |

| [7]        | 0x0           | Reserved.                                             |                      |  |  |

| Address:   | 0xf07         | RW                                                    | Default: 0x40        |  |  |

| [0]        | 0x0           | Enable prima                                          | ary clock.           |  |  |

| [1]        | 0x0           | Analog clock                                          | enable.              |  |  |

| [2]        | 0x0           | ADC top leve                                          | el clock divider.    |  |  |

| [3]        | 0x0           | Reserved.                                             |                      |  |  |

| راحا       |               | Reserved.                                             |                      |  |  |

| [4]        | 0x0           | Reserved.                                             |                      |  |  |

|            | 0x0<br>0x0    | Reserved.                                             |                      |  |  |

| [4]        |               | Reserved.                                             | enerator reset.      |  |  |

| Address: | 0xf0b | RW                      | Default: 0x24             |

|----------|-------|-------------------------|---------------------------|

| [2:0]    | 0x4   | Clock rece              | iver bias.                |

| [5:3]    | 0x4   | ADC maste               | er bias.                  |

| Address: | 0xf0f | RW                      | Default: 0x28             |

| [1:0]    | 0x0   | Clock divid             | ler.                      |

| [3:2]    | 0x2   | Clock dela              | у.                        |

| [5:4]    | 0x2   | Reserved.               |                           |

| Address: | 0xf11 | RW                      | Default: 0x0b             |

| [2:0]    | 0x3   | Main bias.              |                           |

| [4:3]    | 0x1   | Input comr              | mon mode level.           |

| Address: | 0xf27 | RW                      | Default: 0x04             |

| [5:0]    | 0x04  | Dither ena              | ble.                      |

| Address: | 0xdc1 | RW                      | Default: 0xbfff           |

| [0]      | 0x1   | Enable.                 |                           |

| [1]      | 0x1   | Clock enal              | ple.                      |

| [2]      | 0x1   | Soft reset.             |                           |

| [3]      | 0x1   | Reserved.               |                           |

| [4]      | 0x1   | Calibration soft reset. |                           |

| [5]      | 0x1   | Reserved.               |                           |

| [6]      | 0x1   | Reserved.               |                           |

| [10:7]   | 0xf   | Enable ma               | sk for en_adc pin.        |

| [15:11]  | 0x17  | Sleep mas               | k for sleep pin.          |

| Address: | 0xdc3 | RW                      | Default: 0x0000           |

| [3:0]    | 0x0   | Clock phas              | Se.                       |

| [11:4]   | 0x00  | Clock fine              | delay.                    |

| [12]     | 0x0   | Enable fine             | e delay register control. |

| [13]     | 0x0   | Input clock             | polarity switch.          |

| [14]     | 0x0   | Output clo              | ck polarity switch.       |

| Address: | 0xde1 | RW                      | Default: 0xbb28           |

| [7:0]    | 0x28  | Calibration length.     |                           |

| [8]      | 0x1   | Enable calibration.     |                           |

| [9]      | 0x1   | Foreground calibration. |                           |

| [14:10]  | 0x0   | Reserved.               |                           |

| [15]     | 0x1   | Enable reta             | ain mode.                 |

| Address: | 0xde3 | RW                      | Default: 0x8              |

| [2:0]    | 0x0   | Reserved.               | •                         |

| [3]      | 0x1   | Enable sta              | ge calibration.           |

23 | Datasheet www.silannasemi.com Doc. No. 11724, Rev. 2.0

| Address:   | 0xcc1 | RW                                  | Default: 0xbfff    |

|------------|-------|-------------------------------------|--------------------|

| [0]        | 0x1   | Enable.                             |                    |

| [1]        | 0x1   | Clock enabl                         | e.                 |

| [2]        | 0x1   | Soft reset.                         |                    |

| [3]        | 0x1   | Reserved.                           |                    |

| [4]        | 0x1   | Calibration s                       | soft reset.        |

| [5]        | 0x1   | Reserved.                           |                    |

| [6]        | 0x1   | Reserved.                           |                    |

| [10:7]     | 0xf   | Enable mas                          | k for en_adc pin.  |

| [15:11]    | 0x17  | Sleep mask                          | for sleep pin.     |

|            |       |                                     |                    |

| Address:   | 0xcc3 | RW                                  | Default: 0x0000    |

| [3:0]      | 0x0   | Clock phase                         |                    |

| [11:4]     | 0x00  | Clock fine delay.                   |                    |

| [12]       | 0x0   | Enable fine delay register control. |                    |

| [13]       | 0x0   | Input clock polarity switch.        |                    |

| [14]       | 0x0   | Output clock                        | k polarity switch. |

|            |       | 1                                   |                    |

| Address: ( |       | RW                                  | Default: 0xbb28    |

| [7:0]      | 0x28  | Calibration I                       |                    |

| [8]        | 0x1   | Enable calib                        | oration.           |

| [9]        | 0x1   | Foreground calibration.             |                    |

| [14:10]    | 0x0   | Reserved.                           |                    |

| [15]       | 0x1   | Enable retain mode.                 |                    |

|            |       | 1                                   |                    |

| Address:   | 0xce3 | RW                                  | Default: 0x8       |

| [2:0]      | 0x0   | Reserved.                           |                    |

| [3]        | 0x1   | Enable stage calibration.           |                    |

# **ORDERING INFORMATION**

| Base Part No. | Orderable Part No.<br>Full Tray | Orderable Part No.<br>Tray with 50Pcs | Orderable Part No.<br>Reel with 750pcs |

|---------------|---------------------------------|---------------------------------------|----------------------------------------|

| SD9629-20     | SD9629-20-A-QA5-TC              | SD9629-20-A-QA5-TA                    | SD9629-20-A-QA5-RD                     |

|               |                                 |                                       |                                        |

| EVK  | Part No.  |

|------|-----------|

| CMOS | SDE9629-C |

|      |           |

This product is protected by several U.S. Patents (www.silannasemi.com/patents).

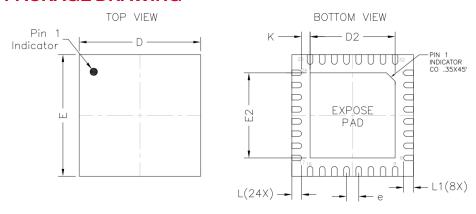

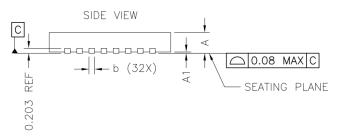

## **PACKAGE DRAWING**

Figure 23: Package Dimensions.

| DIMENSION TABLE |          |         |         |  |

|-----------------|----------|---------|---------|--|

| SYMBOL          | MINIMUM  | NOMINAL | MAXIMUM |  |

| A               | 0.70     | 0.75    | 0.80    |  |

| A1              | 0.00     | 0.02    | 0.05    |  |

| b               | 0.20     | 0.25    | 0.30    |  |

| D               | 4.90     | 5.00    | 5.10    |  |

| D2              | 3.45     | 3.50    | 3.55    |  |

| E               | 4.90     | 5.00    | 5.10    |  |

| E2              | 3.45     | 3.50    | 3.55    |  |

| е               | 0.50 BSC |         |         |  |

| L               | 0.35     | 0.40    | 0.45    |  |

| L1              | 0.33     | 0.38    | 0.43    |  |

| K               | 0.20     | _       | _       |  |

| N               | 32       |         |         |  |

- NOTE:

1. Reference Doc: GRT Doc;:JI-1032-001-24 REV 24 QTY:16/17

Package Type: JEDEC OUTLINE-MO-220, Pack. Code WQFN(X532)

PAD SIZE:B154X15\*MIL

2. Dimensioning and tolerancing conform to ASME Y14.5-2009.

3. Ill

3. Ill

4. N is the foot an in millimeters.

4. N is the foot another of terminals.

5. Unilateral coplanarity zone applies to the exposed part as well as the terminals.

6. Lead Finish: 100% Sn.

# **REVISION HISTORY**

| Version | Date          | Comment                                                                                                       |

|---------|---------------|---------------------------------------------------------------------------------------------------------------|

| 1.0     | June 19, 2025 | Initial Release.                                                                                              |

| 2.0     | July 30, 2025 | Filled missing specifications. Changed RBIAS resistor to $30k\Omega$ . Improved timing diagrams. Fixed typos. |

|         |               |                                                                                                               |

Silanna Semiconductor Proprietary and Confidential

Information furnished by Silanna Semiconductor is believed to be accurate and reliable. However, no responsibility is assumed for its use. Silanna Semiconductor makes no representation that the interconnection of its circuits as described herein will not infringe on existing patents rights. Specifications subject to change without notice.